# HOPERF

# CMT8602X

#### Reinforced Isolation Dual-Channel Gate Driver

# Features

- General: dual channel low side, dual channel high side or half-bridge driver

- Junction temperature range: -40°C to 125°C

- Up to 4-A peak source and 6-A peak sink output

- 3V to 5.5V VCCI working range, can be connected digital and analog controller

- CMTI greater than 150 kV/us

- Isolated layer life > 40 years

- TLL and CMOS compatible

- Up to 30V VDD output drive voltage

- 9V and 13V VDD UVLO option

- Switching parameters:

- 40 ns typical propagation delay

- 25 ns minimum pulse width

- 5 ns maximum delay matching

- 9 ns maximum pulse-width distortion

- Programmable overlap and dead time

- Suppress input pulses and noise transients < 25ns

- Fast disable the power sequence

- Safety-related certifications:

- 8000-V<sub>PK</sub> reinforced isolation per DIN V VDE V 0884-11:2017-01

- 5700-V<sub>RMS</sub> isolation for 1 minute per UL 1577

- CSA certified in accordance with IEC 60950-1 and IEC 62368-1, IEC 61010-1 and IEC 60601-1 terminal equipment standards

- CQC certification per GB4943.1-2011 (Planned)

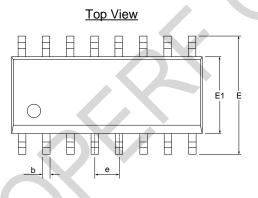

- Applied in SOW14 / SOW16 / SOP16 packages

# Application

- HEV and EV battery chargers

- Isolated converters in AC-to-DC and DC-to-DC power supplies

- Motor drives and inverters

- LED lighting

- Sensor heating

- Uninterruptible power supply (UPS)

# Description

The CMT8602X device is an isolated dual channel gate driver with programmable dead time and wide temperature range. This device exhibits consistent performance and robustness under extreme temperature conditions. It is designed with 4-A peak- source and 6-A peak-sink current to drive 2MHz power MOSFET, IGBT, and SIC MOSEFT, which owns character of first-class propagation delay and pulse width distortion.

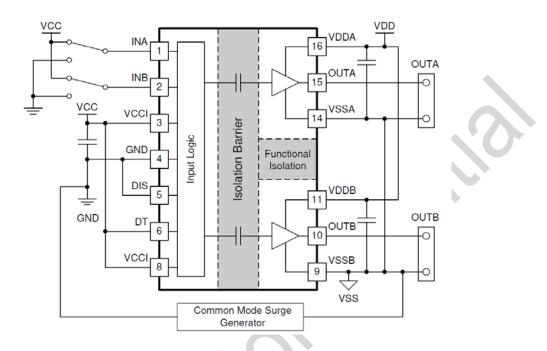

The input side is isolated from the two output drivers by a 5.7  $kV_{RMS}$  isolation barrier, with 150 kV/us common-mode transient immunity (CMTI). Internal functional isolation between the two side drives, supports operating voltages up to 1500V<sub>DC</sub>.

The CMT8602X can be configured as two low-side drivers, two high-side drivers, or a half-bridge driver. The disabled pins close the 2 outputs simultaneously when it is set to high level, while operates the device at open or grounded state. As a failsafe mechanism, the primary side logic failure forces both outputs to be low.

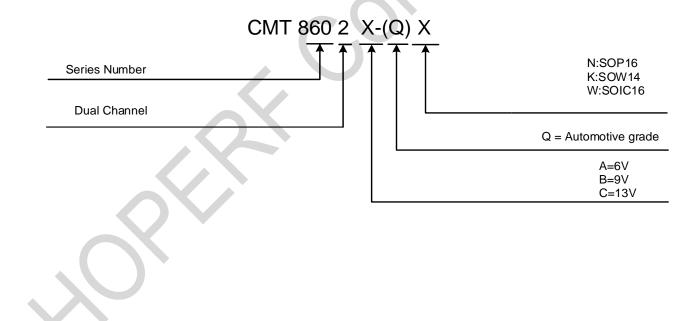

# **Ordering Information**

| Part No.   | Package | Minimum<br>Order Quantity |

|------------|---------|---------------------------|

| CMT8602X-K | SOW14   | 1000                      |

| CMT8602X-W | SOW16   | 1000                      |

| CMT8602X-N | SOP16   | 3000                      |

#### **Table of Contents**

| Fe | eatures                                                                                  | 1    |

|----|------------------------------------------------------------------------------------------|------|

| A  | oplication                                                                               | 1    |

| De | escription                                                                               | 1    |

| 1  | Specifications                                                                           | 4    |

|    | •                                                                                        |      |

|    | <ul><li>1.1 Recommended Operating Ratings</li><li>1.2 Absolute Maximum Ratings</li></ul> |      |

|    | 1.3 ESD Ratings                                                                          |      |

|    | 1.4 Thermal Information                                                                  |      |

|    | 1.5     Power Ratings                                                                    |      |

|    | 1.6     Insulation Specifications.                                                       |      |

|    | 1.7 Safety-Related Certifications                                                        | 7    |

|    | 1.8 Safety-Limiting Values                                                               | 7    |

|    | 1.9 Electrical Characteristics                                                           |      |

|    | 1.10 Switching Characteristics                                                           |      |

|    | 1.11 Typical Characteristics                                                             |      |

| 2  | Pin Description                                                                          |      |

| 3  | Parameter Measurement Information                                                        | 15   |

| 5  |                                                                                          |      |

|    |                                                                                          |      |

|    | 3.2 Propagation Delay and Pulse Width Distortion                                         |      |

|    | 3.3 Rising and Falling Time                                                              |      |

|    | 3.4 Input and Disable Response Time                                                      |      |

|    | 3.5 Programmable Dead Time                                                               |      |

|    | 3.6 Power-up UVLO Delay to OUTPUT                                                        |      |

|    | 3.7 CMTI Testing                                                                         |      |

| 4  | Function Description                                                                     | 18   |

|    | 4.1 Function Overview                                                                    |      |

|    | 4.2 Functional Block Diagram                                                             | . 19 |

|    | 4.3 Feature Description                                                                  |      |

|    | 4.3.1 VDD, VCCI, and Under Voltage Lock Out (UVLO)                                       |      |

|    | 4.3.2 Input and Output Logic Table                                                       |      |

|    | 4.3.3 Input Stage<br>4.3.4 Output Stage                                                  |      |

|    | 4.4 Device Functional Modes                                                              |      |

|    | 4.4.1 Disable Pin                                                                        |      |

|    | 4.4.2 Programmable Dead Time (DT) Pin                                                    |      |

| 5  | Application and Implementation                                                           |      |

|    | 5.1 Application Information                                                              |      |

|    | 5.2 Typication information                                                               |      |

| 6  | Power Supply Recommendations                                                             |      |

| _  |                                                                                          |      |

| 7  | PCB Layout                                                                               |      |

|    | 7.1 Layout Guidelines                                                                    |      |

|    | 7.1.1 Component Placement Considerations                                                 | . 25 |

|    | 7.1.2 Grounding Considerations    | 25 |

|----|-----------------------------------|----|

|    | 7.1.3 High Voltage Considerations | 25 |

|    | 7.1.4 Thermal Considerations      | 25 |

|    | 7.2 Layout Example                | 26 |

| 8  | Ordering Information              | 27 |

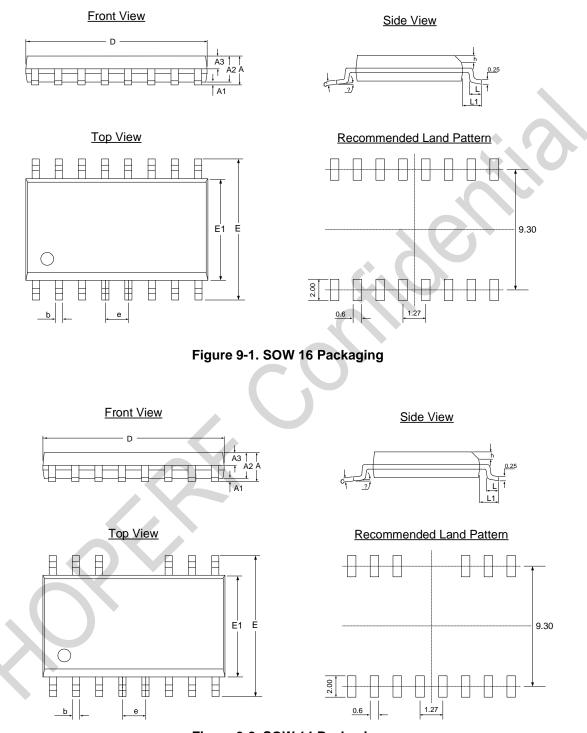

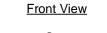

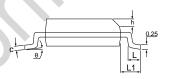

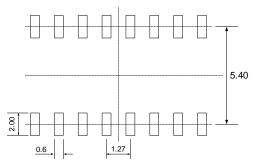

| 9  | Packaging Information             | 28 |

| 10 | Revise History                    | 31 |

| 11 | Contacts                          | 32 |

# **1** Specifications

### **1.1 Recommended Operating Ratings**

Over operating free-air temperature range (unless otherwise noted).

| Parameter                 | Symbol                              | Condition | Min. | Тур. | Max. | Unit |

|---------------------------|-------------------------------------|-----------|------|------|------|------|

| VCCI Input supply voltage | V <sub>CCI</sub>                    |           | 3    |      | 5.5  | V    |

| Driver output bias supply | V <sub>DDA</sub> , V <sub>DDB</sub> | CMT8602X  | 9    |      | 30   | V    |

| Junction Temperature      | TJ                                  |           | -40  |      | 150  | °C   |

| Ambient Temperature       | T <sub>A</sub>                      |           | -40  |      | 125  | °C   |

#### **Table 1-1. Recommended Operating Ratings**

### 1.2 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted).

| Parameter                               | Symbol                                                                  | Condition | Min. | Тур. | Max.                                                | Unit |

|-----------------------------------------|-------------------------------------------------------------------------|-----------|------|------|-----------------------------------------------------|------|

| Input bias pin supply voltage           | V <sub>CCI</sub> to GND                                                 |           | -0.3 |      | 5.5                                                 | V    |

| Driver bias supply                      | V <sub>DDA</sub> -V <sub>SSA</sub> , V <sub>DDB</sub> -V <sub>SSB</sub> |           | -0.3 |      | 35                                                  | V    |

|                                         | OUTA to $V_{SSA}$ , OUTB to $V_{SSB}$                                   |           | -0.3 |      | V <sub>VDDA</sub> + 0.3,<br>V <sub>VDDB</sub> + 0.3 | V    |

| Output signal voltage                   | OUTA to $V_{SSA}$ , OUTB to $V_{SSB}$ , Transient for 200 ns            |           | -2   |      | $V_{VDDA}$ +0.3, $V_{VDDB}$ +0.3                    | V    |

|                                         | INA, INB, DIS and DT to GND                                             |           | -0.3 |      | V <sub>VCCI</sub> + 0.3                             | V    |

| Input signal voltage                    | INA, INB Transient for 50ns                                             |           | -5   |      | V <sub>VCCI</sub> + 0.3                             | V    |

| Channel to channel<br>isolation voltage |                                                                         |           |      | 1500 | V                                                   |      |

| Junction temperature                    | TJ                                                                      |           | -40  |      | 150                                                 | °C   |

| Storage temperature                     | T <sub>stg</sub>                                                        |           | -65  |      | 150                                                 | °C   |

| Table 1-2. | Absolute | Maximum | Ratings <sup>[1]</sup> |

|------------|----------|---------|------------------------|

|------------|----------|---------|------------------------|

Notes:

[1]. Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent performance degradation or loss of functionality.

### 1.3 ESD Ratings

#### Table 1-3. ESD Ratings

| Parameter                                                                                                                                                                                                                                    | Symbol           | Condition                                                                         | Max.  | Unit |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------|-------|------|--|--|

|                                                                                                                                                                                                                                              |                  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>[1]</sup>                 | ±4000 |      |  |  |

| Electrostatic<br>Discharge                                                                                                                                                                                                                   | V <sub>ESD</sub> | Charged-device model (CDM), per JEDEC specification JESD22- V C101 <sup>[2]</sup> | ±1500 | V    |  |  |

| Notes:<br>[1]. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.<br>[2]. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. |                  |                                                                                   |       |      |  |  |

### **1.4 Thermal Information**

### Table 1-4. Thermal Information

| Parameter                                    | Symbol                | СМТ8602Х    | Unit |  |

|----------------------------------------------|-----------------------|-------------|------|--|

| i diameter                                   | Gymbol                | SOW16/SOW14 | onit |  |

| Junction-to-ambient thermal resistance       | R <sub>eja</sub>      | 97.3        | °C/W |  |

| Junction-to-case (top) thermal resistance    | R <sub>0JC(top)</sub> | 23.3        | °C/W |  |

| Junction-to-top characterization parameter   | Ψ <sub>JT</sub>       | 35          | °C/W |  |

| Junction-to-board characterization parameter | Ψ <sub>JB</sub>       | 34          | °C/W |  |

### 1.5 Power Ratings

#### Table 1-5. Power Information

| Parameter                             | Symbol          | Condition                                           | СМТ8602Х | Unit |

|---------------------------------------|-----------------|-----------------------------------------------------|----------|------|

| Power dissipation                     | PD              | V <sub>CCI</sub> =5.5 V, V <sub>DDA/B</sub> = 13 V, | 1.33     | W    |

| Power dissipation by transmitter side | P <sub>DI</sub> | INA/B = 3.3 V, 2 MHz 50% duty                       | 0.01     | W    |

| Power dissipation by each driver side | $P_{DA},P_{DB}$ | cycle square wave 1.0 nF load.                      | 0.66     | W    |

# **1.6 Insulation Specifications**

| Parameter                                           | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                        | Condition                                                                                                                                                                                                                                                             | Value | Unit             |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|

| External clearance [1]                              | CLR                                                                                                                                                                                                                                                                                                                                                                                                                           | Shortest pin-to-pin distance through air                                                                                                                                                                                                                              | > 8   | mm               |

| External creepage <sup>[1]</sup>                    | CPG                                                                                                                                                                                                                                                                                                                                                                                                                           | Shortest pin-to-pin distance across the package surface                                                                                                                                                                                                               | > 8   | mm               |

| Distance through insulation                         | DTI                                                                                                                                                                                                                                                                                                                                                                                                                           | Minimum internal gap (internal clearance) of the double insulation (2 × 8.5 μm)                                                                                                                                                                                       | >30   | μm               |

| Comparative tracking index                          | СТІ                                                                                                                                                                                                                                                                                                                                                                                                                           | DIN EN 60112 (VDE 0303-11);<br>IEC 60112                                                                                                                                                                                                                              | > 600 | V                |

| Material group                                      |                                                                                                                                                                                                                                                                                                                                                                                                                               | According to IEC 60664-1                                                                                                                                                                                                                                              | I     |                  |

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                               | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                                                                            | I-IV  |                  |

| Overvoltage category per IEC 60664-1                |                                                                                                                                                                                                                                                                                                                                                                                                                               | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                                                                                                           | 1-111 |                  |

| DIN V VDE V 0884-11 (VDE V 0884-11)                 | : <b>2017-01</b> <sup>[2]</sup>                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                       |       |                  |

| Maximum repetitive peak isolation voltage           | VIORM                                                                                                                                                                                                                                                                                                                                                                                                                         | AC voltage (bipolar)                                                                                                                                                                                                                                                  | 2121  | V <sub>PK</sub>  |

| Maximum working isolation voltage                   | V <sub>IOWM</sub>                                                                                                                                                                                                                                                                                                                                                                                                             | AC voltage (sine wave); time<br>dependent dielectric breakdown<br>(TDDB), test                                                                                                                                                                                        | 1500  | V <sub>RMS</sub> |

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                               | DC voltage                                                                                                                                                                                                                                                            | 2121  | V <sub>DC</sub>  |

| Maximum transient isolation voltage                 | $V_{\text{IOTM}} = V_{\text{IOTM}}, t = 60 \text{ s}$ $V_{\text{IOTM}} = 1.2 \times V_{\text{IOTM}}, t = 1 \text{ s} (100\%)$ $V_{\text{TEST}} = 1.2 \times V_{\text{IOTM}}, t = 1 \text{ s} (100\%)$ $V_{\text{IOTM}} = 1.2 \times V_{\text{IOTM}}, t = 1 \text{ s} (100\%)$ $V_{\text{IOTM}} = 1.2 \times V_{\text{IOTM}}, t = 1 \text{ s} (100\%)$ $V_{\text{IOTM}} = 1.2 \times V_{\text{IOTM}}, t = 1 \text{ s} (100\%)$ |                                                                                                                                                                                                                                                                       | 8000  | V <sub>PK</sub>  |

| Maximum surge isolation voltage <sup>[3]</sup>      | V <sub>IOSM</sub>                                                                                                                                                                                                                                                                                                                                                                                                             | Test method per IEC 62368-1,<br>1.2/50 μs waveform,<br>V <sub>TEST</sub> = 1.6 × V <sub>IOSM</sub> = 12800 V <sub>PK</sub><br>(qualification)                                                                                                                         | 8000  | V <sub>PK</sub>  |

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                               | Method a, After I/O safety test<br>subgroup 2/3. Vini = V <sub>IOTM</sub> , tini =<br>60  s;<br>$V_{pd(m)} = 1.2 \text{ X } V_{IORM} = 2545 \text{ V}_{PK}, t_m$<br>= 10 s                                                                                            | <5    |                  |

| Apparent charge <sup>[4]</sup>                      | q <sub>pd</sub>                                                                                                                                                                                                                                                                                                                                                                                                               | Method a, After environmental tests subgroup 1. Vini = VIOTM, tini = 60 s; $V_{pd(m)}$ = 1.6 X V <sub>IORM</sub> = 3394 V <sub>PK</sub> , t <sub>m</sub> = 10 s                                                                                                       | <5    | рC               |

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                               | $\label{eq:constraint} \begin{array}{l} \mbox{Method b1; At routine test (100\% production) and preconditioning (type test) } \\ V_{ini} = 1.2 \times V_{IOTM}; t_{ini} = 1 \ s; \\ V_{pd(m)} = 1.875 \ ^* \ V_{IORM} = 3977 \ V_{PK} \ , \\ t_m = 1 \ s \end{array}$ | <5    |                  |

| Barrier capacitance, input to output <sup>[5]</sup> | C <sub>IO</sub>                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>IO</sub> = 0.4 sin (2πft), f =1 MHz                                                                                                                                                                                                                            | 1.2   | pF               |

#### Table 1-6. Thermal Information

| Parameter                                            | Symbol                            | Condition                                                      | Value              | Unit             |

|------------------------------------------------------|-----------------------------------|----------------------------------------------------------------|--------------------|------------------|

|                                                      |                                   | $V_{IO} = 500 \text{ V}$ at $T_A = 25^{\circ}\text{C}$         | > 10 <sup>12</sup> |                  |

| Isolation resistance, input to output <sup>[5]</sup> | R <sub>IO</sub>                   | $V_{IO}$ = 500 V at 100°C ≤ $T_A$ ≤ 125°C                      | > 10 <sup>11</sup> | Ω                |

|                                                      |                                   | $V_{IO} = 500 \text{ V} \text{ at } T_S = 150^{\circ}\text{C}$ | > 10 <sup>9</sup>  |                  |

| Pollution degree                                     |                                   |                                                                | 2                  |                  |

| Climatic category                                    |                                   |                                                                | 40/125/21          |                  |

| UL 1577                                              |                                   |                                                                |                    |                  |

| V <sub>ISO</sub>                                     | Withstand<br>isolation<br>voltage |                                                                | 5700               | V <sub>RMS</sub> |

| Notes:                                               |                                   | ·                                                              |                    |                  |

- [1]. Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed circuit board are used to help increase these specifications..

- [2]. This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- [3]. Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- [4]. Apparent charge is electrical discharge caused by a partial discharge (pd).

- [5]. All pins on each side of the barrier tied together creating a two-pin device.

### 1.7 Safety-Related Certifications

#### Table 1-7. Safety-Related Certifications

| VDE                                                    | CSA                                                                | UL                                                                                     | CQC                                          | TUV                                                                                    |

|--------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------|

| DIN VDE V0884-<br>11:2017-01<br>( Patents<br>pending ) | IEC 60950-1, IEC 62368-1<br>and IEC 61010-1<br>( Patents pending ) | Recognized under<br>UL 1577 Component<br>Recognition<br>Program<br>( Patents pending ) | GB 4943.1-2011                               | EN 61010-1:2010 (3rd<br>Ed) and EN 60950-<br>1:2006/A2:<br>2013<br>( Patents pending ) |

| Certificate number:<br>pending                         | Master contract number:<br>pending                                 | File number:<br>pending                                                                | Certificate number:<br>CQC11-471543-<br>2022 | Client ID number:<br>pending                                                           |

### 1.8 Safety-Limiting Values

Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry.

| Parameter      | Symbol | TEST CONDITIONS                                                                                                | SIDE                  | MIN | ΤΥΡ | MAX | UNIT |

|----------------|--------|----------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-----|------|

| Safety output  | Is     | $\theta_{JA} = 97.3 \text{ °C/W}, V_{VDDA/B} = 15 \text{ V},$<br>T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C | DRIVER A,<br>DRIVER B |     |     | TBD | mA   |

| supply current | 13     | $\theta_{JA} = 97.3^{\circ}C/W, V_{DDA/B} = 30 V,$<br>T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C            | DRIVER A,             |     |     | TBD | mA   |

#### Table 1-8. Safety-Limiting Values

|                                      |    |                                        | DRIVER B |  |     |    |

|--------------------------------------|----|----------------------------------------|----------|--|-----|----|

|                                      |    |                                        | INPUT    |  | TBD |    |

| Safety supply                        | Р  | Dout 07 280 MM TA 2580 TA 15080        | DRIVER A |  | TBD | mW |

| power                                | Ps | RθJA = 97.3°C/W, TA = 25°C, TJ = 150°C | DRIVER B |  | TBD |    |

|                                      |    |                                        | TOTAL    |  | TBD |    |

| Safety<br>temperature <sup>[1]</sup> | Ts |                                        |          |  | TBD | °C |

Notes:

[1]. The maximum safety temperature, T<sub>S</sub>, has the same value as the maximum junction temperature, T<sub>J</sub>, specified for the device. The IS and PS parameters represent the safety current and safety power respectively. The maximum limits of I<sub>S</sub> and PS should not be exceeded. These limits vary with the ambient temperature, T<sub>A</sub>.

The junction-to-air thermal resistance,  $R_{\theta JA}$ , in the Section 1.4 table is that of a device installed on a high-K test board for leaded surface-mount packages. Use these equations to calculate the value for each parameter:

$T_J = T_A + R_{\theta JA} \times P$ , where P is the power dissipated in the device.

$T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$ , where  $T_{J(max)}$  is the maximum allowed junction temperature.  $P_S = I_S \times V_I$ , where  $V_I$  is the maximum input voltage.

### **1.9 Electrical Characteristics**

$V_{VCCI} = 3.3 \text{ V or } 5.0 \text{ V}, 0.1 - \mu\text{F}$  capacitor from VCCI to GND,  $V_{VDDA} = V_{VDDB} = 15 \text{ V}, 1 - \mu\text{F}$  capacitor from  $V_{DDA}$  and  $V_{DDB}$  to  $V_{SSA}$  and  $V_{SSB}$ ,  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  unless otherwise noted<sup>[1]</sup>.

| Parameter                                               | Symbol                                         | Condition                                                            | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------|------|------|------|------|

| SUPPLY CURRENTS                                         |                                                |                                                                      |      |      |      |      |

| V <sub>CCI</sub> quiescent current                      | I <sub>vcci</sub>                              | $V_{\text{INA}} = 0 \text{ V}, \text{ V}_{\text{INB}} = 0 \text{ V}$ |      | 1.4  | 2.0  | mA   |

| V <sub>DDA</sub> and V <sub>DDB</sub> quiescent current | I <sub>VDDA</sub> , I <sub>VDDB</sub>          | $V_{INA} = 0 V, V_{INB} = 0 V$                                       |      | 1.1  | 1.8  | mA   |

| V <sub>CCI</sub> operating current                      | I <sub>VCCI</sub>                              | current per channel<br>$C_{OUT} = 100 \text{ pF}$<br>(f = 500 kHz)   |      | 2.0  |      | mA   |

| $V_{\text{DDA}}$ and $V_{\text{DDB}}$ operating current | I <sub>vdda</sub> , I <sub>vddb</sub>          | current per channel $C_{OUT}$ = 100 pF (f = 500 kHz)                 |      | 3.3  |      | mA   |

| VCCI SUPPLY VOLTAGE UND                                 | ERVOLTAGE TH                                   | RESHOLDS                                                             |      |      | •    | 1    |

| Rising threshold                                        | V <sub>VCCI_ON</sub>                           |                                                                      | 2.55 | 2.7  | 2.85 | V    |

| Falling threshold                                       | V <sub>VCCI_OFF</sub>                          |                                                                      | 2.35 | 2.5  | 2.65 | V    |

| Threshold hysteresis                                    | V <sub>VCCI_HYS</sub>                          |                                                                      |      | 0.2  |      | V    |

| VDD UVLO THRESHOLDS                                     | •                                              |                                                                      |      | •    | •    |      |

| Rising threshold $V_{DDA_ON}$ , $V_{DDB_ON}$            | V <sub>VDDA_ON</sub><br>V <sub>VDDB_ON</sub>   |                                                                      | 8    | 8.5  | 9    | V    |

| Falling threshold $V_{DDA_OFF}$ , $V_{DDB_OFF}$         | V <sub>VDDA_OFF</sub><br>V <sub>VDDB_OFF</sub> |                                                                      | 7.5  | 8    | 8.5  | V    |

#### Table 1-9. Recommended Operating Ratings<sup>[1]</sup>

| Threshold hysteresis            | V <sub>vdda_hys</sub><br>V <sub>vddb_hys</sub>                           |                                                                                                                                  |           | 0.5          |             | V  |

|---------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|-------------|----|

| INA, INB AND DISABLE            |                                                                          |                                                                                                                                  |           |              |             |    |

| Input high threshold voltage    | V <sub>inah</sub><br>V <sub>inbh</sub><br>V <sub>dish</sub>              |                                                                                                                                  | 1.6       | 1.8          | 2           | V  |

| Input low threshold voltage     | V <sub>INAL,</sub> V <sub>INBL,</sub><br>V <sub>DISL</sub>               |                                                                                                                                  | 0.8       | 1            | 1.2         | V  |

| Input threshold hysteresis      | V <sub>INA_HYS</sub> ,<br>V <sub>INB_HYS</sub> ,<br>V <sub>DIS_HYS</sub> |                                                                                                                                  |           | 0.8          | . 0         | V  |

| Vina, Vinb                      | Negative<br>transient, ref<br>to GND, 50 ns<br>pulse                     | Not production tested, bench test only                                                                                           | -5        | ~            |             | v  |

| OUTPUT                          |                                                                          |                                                                                                                                  |           |              |             |    |

| Peak output source current      | I <sub>OA+</sub> , I <sub>OB+</sub>                                      | $C_{VDD} = 10 \ \mu\text{F}, C_{LOAD} =$<br>0.18 \ \mm F, f =<br>1 \ kHz, bench<br>measurement                                   |           | 4            |             | A  |

| Peak output sink current        | I <sub>OA-</sub> , I <sub>OB-</sub>                                      | $I_{OUT} = -10 \text{ mA}, R_{OHA}, R_{OHB}$ do not<br>represent drive pull-up<br>performance                                    |           | 6            |             | A  |

| Output resistance at high state | R <sub>oha,</sub> R <sub>ohb</sub>                                       | $I_{OUT} = 10 \text{ mA}, \text{ TA} = 25^{\circ}\text{C}, R_{OHA}, R_{OHB} \text{ do not}$ represent drive pull-up performance. |           | 5            |             | Ω  |

| Output resistance at low state  | R <sub>OLA,</sub> R <sub>OLB</sub>                                       | l <sub>ouτ</sub> = 10 mA,<br>TA = 25°C                                                                                           |           | 0.55         |             | Ω  |

| Output voltage at high state    | V <sub>OHA,</sub> V <sub>OHB</sub>                                       | $V_{VDDA}$ , $V_{VDDB} = 12$ V, $I_{OUT} = -10$ mA, TA = 25°C                                                                    |           | 11.95        |             | V  |

| Output voltage at low state     | $V_{OLA,}^{}V_{OLB}^{}$                                                  | $V_{VDDA}$ , $V_{VDDB} = 12$ V, $I_{OUT}$<br>= 10 mA, TA = 25°C                                                                  |           | 5.5          |             | mV |

| DEAD TIME AND OVERLAP PR        | ROGRAMMING                                                               |                                                                                                                                  |           |              |             |    |

| X ·                             |                                                                          | DT pin tied to $V_{CCI}$                                                                                                         | Overlap o | determined b | by INA, INB | -  |

| Dead time                       | DT                                                                       | DT pin is left open, min<br>spec characterized only,<br>tested for outliers                                                      | 0         | 8            | 15          | ns |

|                                 |                                                                          | R <sub>DT</sub> = 20 kΩ                                                                                                          | 160       | 200          | 240         |    |

Notes:

<sup>[1].</sup> Current direction in the testing conditions is defined to be positive into the pin and negative out of the specified terminal (unless otherwise noted)

### **1.10 Switching Characteristics**

$V_{VCCI} = 3.3 \text{ V or } 5.5 \text{ V}, 0.1 \text{-}\mu\text{F}$  capacitor from VCCI to GND,  $V_{VDDA} = V_{VDDB} = 15 \text{ V}, 1 \text{-}\mu\text{F}$  capacitor from  $V_{DDA}$  and  $V_{DDB}$  to  $V_{SSA}$  and  $V_{SSB}$ ,  $T_{J} = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  unless otherwise noted.

| PARAMETER                                                                               | Symbol                    | TEST CONDITIONS                                                                          | MIN | ТҮР | МАХ | UNIT |

|-----------------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Output rise time, 20% to 80% measured points                                            | t <sub>rise</sub>         | C <sub>OUT</sub> = 1.8 nF                                                                |     | 6   | 16  | ns   |

| Output fall time, 90% to 10% measured points                                            | t <sub>FALL</sub>         | C <sub>OUT</sub> = 1.8 nF                                                                |     | 7   | 12  | ns   |

| Minimum input pulse width                                                               | t <sub>PWmin</sub>        | Output does not change the state if input signal less than $t_{\mbox{PWmin}}$            |     | 25  | 30  | ns   |

| Propagation delay at falling edge                                                       | t <sub>PDHL</sub>         | INx high threshold, V <sub>INH</sub> , to 10% of the output                              | 30  | 40  | 50  | ns   |

| Propagation delay at rising edge                                                        | t <sub>PDLH</sub>         | INx low threshold, $V_{\text{INL}}$ to 90% of the output                                 | 25  | 35  | 45  | ns   |

| Pulse width distortion                                                                  | t <sub>PWD</sub>          | $ \mathbf{t}_{PDLHA} - \mathbf{t}_{PDHLA} , \  \mathbf{t}_{PDLHB} - \mathbf{t}_{PDHLB} $ |     |     | 9   | ns   |

| Propagation delays matching between V <sub>OUTA</sub> , V <sub>OUTB</sub>               | t <sub>DM</sub>           | f = 100 kHz                                                                              |     |     | 5   | ns   |

| V <sub>DDA</sub> , V <sub>DDB</sub> Power-up Delay<br>Time; UVLO Rise to OUTA,<br>OUTB. | t <sub>VCCI+ to OUT</sub> | INA or INB tied to V <sub>CCI</sub>                                                      |     | 100 |     | μs   |

| High-level common-mode transient immunity                                               | CM <sub>H</sub>           | INA and INB both are tied to V <sub>CCI</sub> ; V <sub>CM</sub> =1500 V;                 |     | 150 |     |      |

| Low-level common-mode transient immunity                                                | CM <sub>L</sub>           | INA and INB both are tied to GND; $V_{CM}$ =1500 V;                                      |     | 150 |     | V/ns |

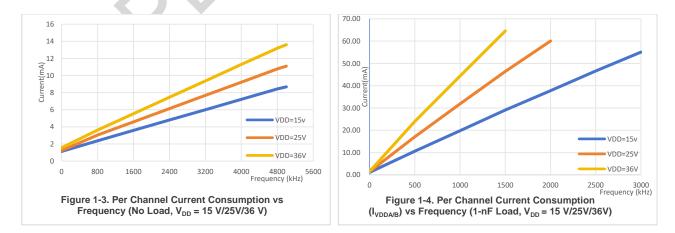

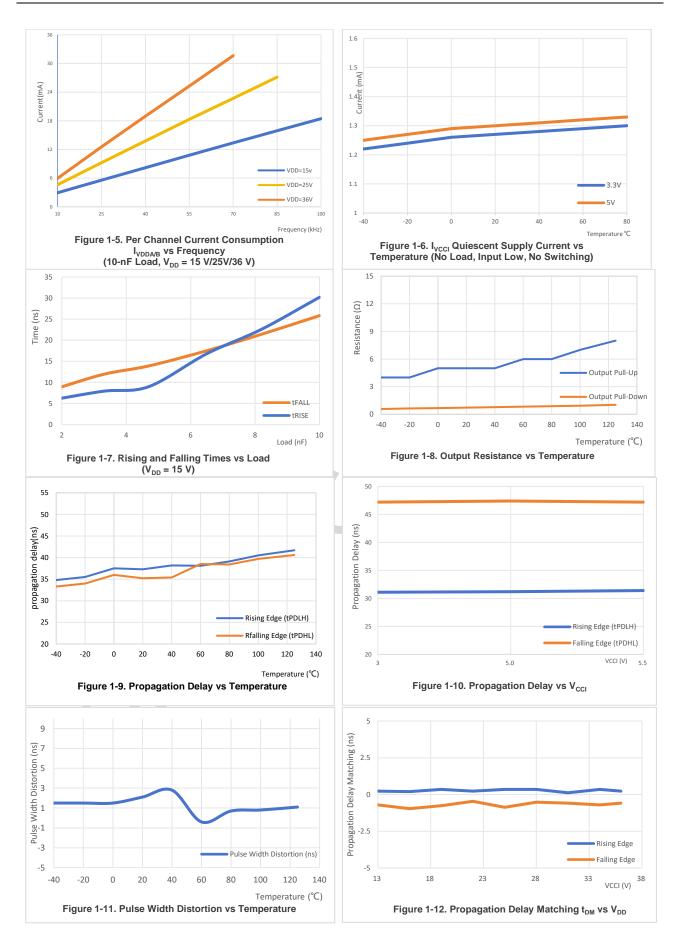

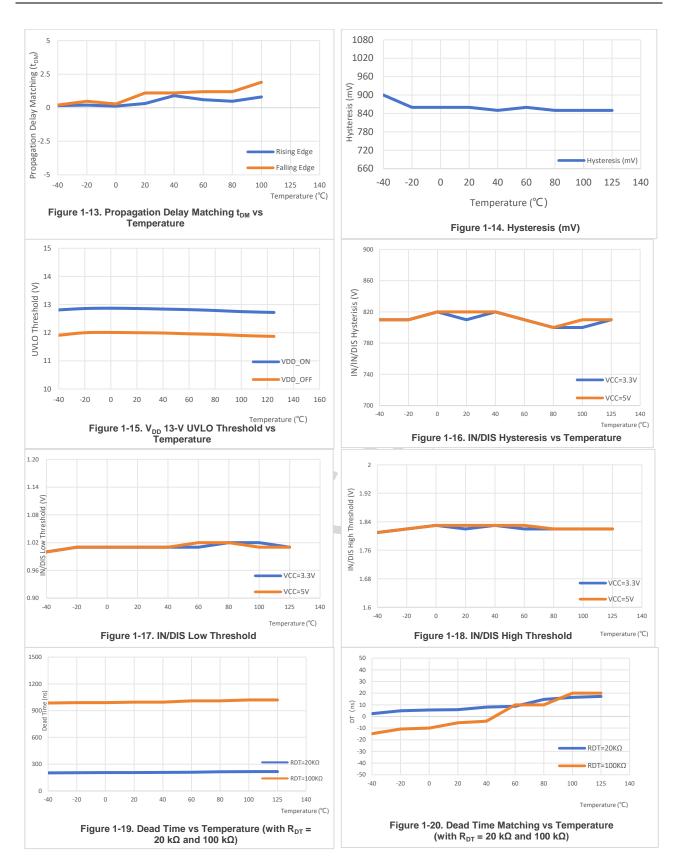

### **1.11 Typical Characteristics**

VDDA = VDDB = 15 V, VCCI = 3.3 V,  $T_{A}$  = 25  $^{\circ}\,$  C,  $C_{L}$  = 0 pF unless otherwise noted.

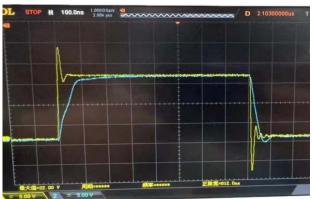

### CMT8602X

Figure 1-21. Typical putput waveforms

# 2 Pin Description

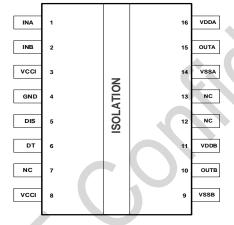

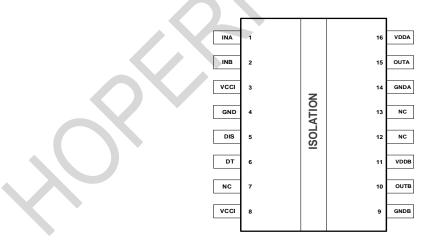

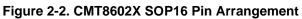

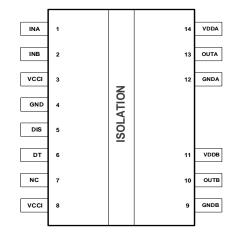

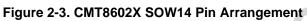

Figure 2-1. CMT8602X SOW16 Pin Arrangement

| Table 2-1. CMT8602X Pin Description | on |  |

|-------------------------------------|----|--|

|       | Pin # |       | Pin  | <b>I/O</b> <sup>[1]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------|-------|------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOW16 | SOW14 | SOP16 | Name | 1/011                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5     | 5     | 5     | DIS  | I                         | Disables both driver outputs if asserted high, enables if set low. It is recommended to tie this pin to ground if not used to achieve better noise immunity. Bypass using a $\approx$ 1-nF low ESR/ESL capacitor close to DIS pin when connecting to a $\mu$ C with distance.                                                                                                                                                      |

| 6     | 6     | 6     | DT   | 1                         | <ul> <li>DT pin configuration:</li> <li>Tying DT to V<sub>CCI</sub> disables the DT feature and allows the outputs to overlap.</li> <li>Placing a resistor (R<sub>DT</sub>) between DT and GND adjusts dead time according to the equation: DT (in ns) = 10 × R<sub>DT</sub> (in kΩ). HOPE recommends bypassing this pin with a ceramic capacitor, 2.2 nF or greater, close to DT pin to achieve better noise immunity.</li> </ul> |

| 4     | 4     | 4     | GND  | Р                         | Primary-side ground reference. All signals in the primary side are referenced to this ground.                                                                                                                                                                                                                                                                                                                                      |

|       | 12    | 14    | GNDA |                           | Side A ground terminal.                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 9     | 9     | GNDB |                           | Side B ground terminal.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1     | 1     | 1     | INA  | I                         | Input signal for A channel. INA input has a TTL/CMOS compatible<br>input threshold. This pin is pulled low internally if left open. It is<br>recommended to tie this pin to ground if not used to achieve better<br>noise immunity.                                                                                                                                                                                                |

| 2     | 2     | 2     | INB  | I                         | Input signal for B channel. INB input has a TTL/CMOS compatible<br>input threshold. This pin is pulled low internally if left open. It is<br>recommended to tie this pin to ground if not used to achieve better<br>noise immunity.                                                                                                                                                                                                |

| 7     |       | 7     | NC   | -                         | No internal connection. This pin can be left floating, tied to $V_{CCI}$ , or tied to GND.                                                                                                                                                                                                                                                                                                                                         |

| 12    |       | 12    | NC   | -                         | No internal connection.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13    | -     | 13    | NC   | -                         | No internal connection.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15    | 13    | 15    | OUTA | 0                         | Output of driver A. Connect to the gate of the A channel FET or IGBT.                                                                                                                                                                                                                                                                                                                                                              |

| 10    | 10    | 10    | OUTB | 0                         | Output of driver B. Connect to the gate of the B channel FET or IGBT.                                                                                                                                                                                                                                                                                                                                                              |

| 3     | 3     | 3     | VCCI | Р                         | Primary-side supply voltage. Locally decoupled to GND using a low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                                                                                                                    |

| 8     | 8     | 8     | VCCI | Р                         | This pin is internally shorted to pin 3.<br>Preference should be given to bypassing pin 3-4 instead of pins 8-4.                                                                                                                                                                                                                                                                                                                   |

| 16    | 14    | 16    | VDDA | Р                         | Secondary-side power for driver A. Locally decoupled to $V_{SSA}$ using a low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                                                                                                        |

| 11    | 11    | 11    | VDDB | Р                         | Secondary-side power for driver B. Locally decoupled to $V_{\text{SSB}}$ using a low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                                                                                                 |

|        | Pin # |       | Pin       | <b>I/O</b> <sup>[1]</sup> | Description                                                                        |

|--------|-------|-------|-----------|---------------------------|------------------------------------------------------------------------------------|

| SOW16  | SOW14 | SOP16 | OP16 Name |                           | Description                                                                        |

| 14     |       |       | VSSA      | Р                         | Ground for secondary-side driver A. Ground reference for secondary side A channel. |

| 9      |       |       | VSSB      | Р                         | Ground for secondary-side driver B. Ground reference for secondary side B channel. |

| Notes: |       |       |           |                           |                                                                                    |

Notes:

[1] P = power, I = input, O = output

# **3** Parameter Measurement Information

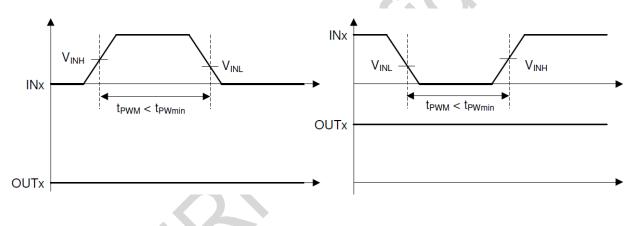

### 3.1 Minimum Pulses

A typical 25-ns deglitch filter removes small input pulses introduced by ground bounce or switching transients. An input pulse with duration longer than  $t_{PWmin}$ , typically 25 ns, must be asserted on INA or INB to guarantee an output state change at OUTA or OUTB. See the 2 figures below for detailed information of the operation of deglitch filter.

Figure 3-1. Deglitch Filter – Turn ON

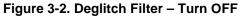

### 3.2 Propagation Delay and Pulse Width Distortion

The figure below shows calculation of pulse width distortion ( $t_{PWD}$ ) and delay matching ( $t_{DM}$ ) from the propagation delays of channels A and B. To measure delay matching, both inputs must be in phase, and the DT pin must be shorted to V<sub>CCI</sub> to enable output overlap.

Figure 3-3. Delay Matching and Pulse Width Distortion

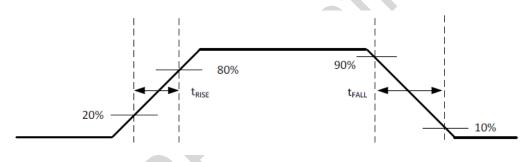

### 3.3 Rising and Falling Time

The figure below shows the criteria for measuring rising ( $t_{\text{RISE}}$ ) and falling ( $t_{\text{FALL}}$ ) time.

Figure 3-4. Rising and Falling Time Criteria

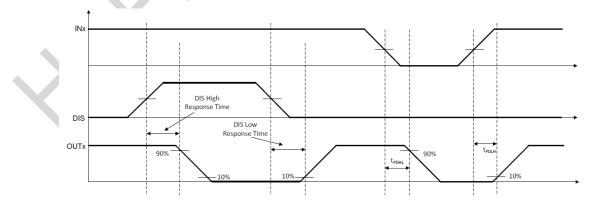

### 3.4 Input and Disable Response Time

The figure below shows the response time of the disable function.

Figure 3-5. Disable Pin Timing

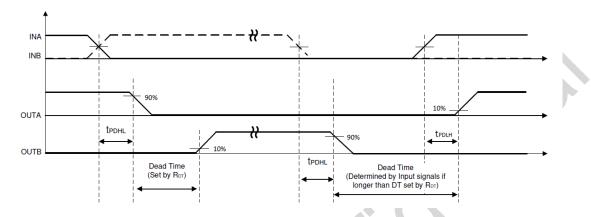

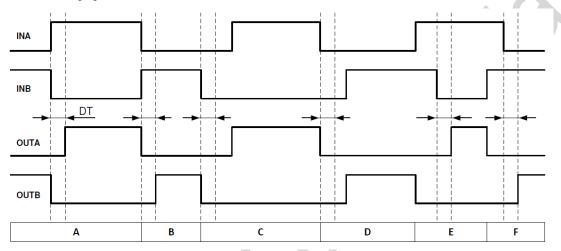

### 3.5 Programmable Dead Time

Tying DT to VCCI disables DT feature and allows the outputs to overlap. Placing a resistor ( $R_{DT}$ ) between DT and GND adjusts dead time according to the equation: DT (in ns) = 10 x  $R_{DT}$  (in k $\Omega$ ). HOPE recommends bypassing this pin with a ceramic capacitor, 2.2 nF or greater, close to DT pin to achieve better noise immunity.

Figure 3-6. Dead Time Switching Parameters

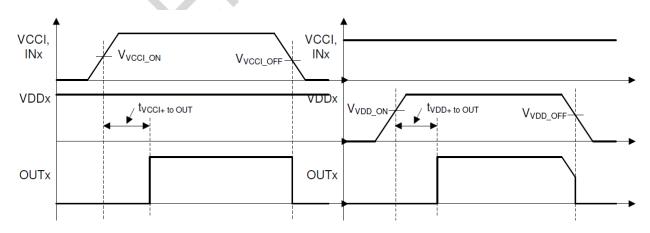

### 3.6 Power-up UVLO Delay to OUTPUT

Before the driver is ready to deliver a proper output state, there is a power-up delay from the UVLO rising edge to output and it is defined as  $t_{VCCI+to OUT}$  for  $V_{CCI}$  UVLO (typically 50us) and  $t_{VDD+to OUT}$  for  $V_{DD}$  UVLO (typically 100 us). It is recommended to consider proper margin before launching PWM signal after the driver's  $V_{CCI}$  and  $V_{DD}$  bias supply is ready. Figure 3-7 and Figure 3-8 show the power-up UVLO delay timing diagram for  $V_{CCI}$  and  $V_{DD}$ . If INA or INB are active before  $V_{CCI}$  or  $V_{DD}$  have crossed above their respective on thresholds, the output will not update until  $t_{VCCI+to OUT}$  or  $t_{VDD+to OUT}$  after  $V_{CCI}$  or  $V_{DD}$  crossing its UVLO rising threshold. However, when either  $V_{CCI}$  or  $V_{DD}$  receive a voltage less than their respective off thresholds, there is <1µs delay, depending on the voltage slew rate on the supply pins, before the outputs are held low. This asymmetric delay is designed to ensure safe operation during  $V_{CCI}$  or  $V_{DD}$  brownouts.

Figure 3-8. V<sub>DDA/B</sub> Power-up UVLO Delay

### 3.7 CMTI Testing

The figure below is a simplified diagram of the CMTI testing configuration.

#### Figure 3-9. Simplified CMTI Testing Setup

# **4** Function Description

### 4.1 Function Overview

In order to switch power transistors rapidly and reduce switching power losses, high-current gate drivers are often placed between the output of control devices and the gates of power transistors. There are several instances where controllers are not capable of delivering sufficient current to drive the gates of power transistors. This is especially the case with digital controllers, since the input signal from the digital controller is often a 3.3V logic signal capable of only delivering a few mA.

The CMT8602X is a flexible dual gate driver which can be configured to fit a variety of power supply and motor drive topologies, as well as drive several types of transistors. The CMT8602X has many features that allow it to integrate well with control circuitry and protect the gates it drives such as: resistor-programmable dead time (DT) control, disable pin, and under voltage lock out (UVLO) for both input and output supplies. The CMT8602X also holds its outputs low when the inputs are left open or when the input pulse duration is too short. The driver inputs are CMOS and TTL compatible for interfacing with digital and analog power controllers alike. Each channel is controlled by its respective input pins (INA and INB), allowing full and independent control of each one of the outputs.

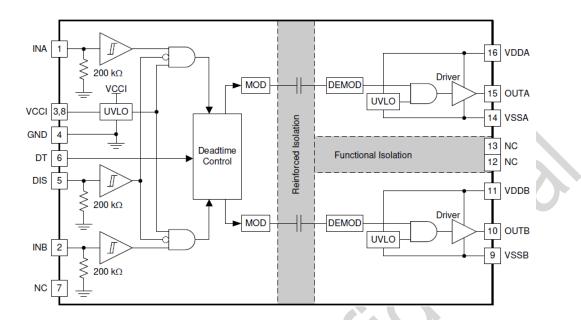

### 4.2 Functional Block Diagram

Figure 4-1. Simplified Representation of Active Pull Down Feature

### 4.3 Feature Description

### 4.3.1 VDD, VCCI, and Under Voltage Lock Out (UVLO)

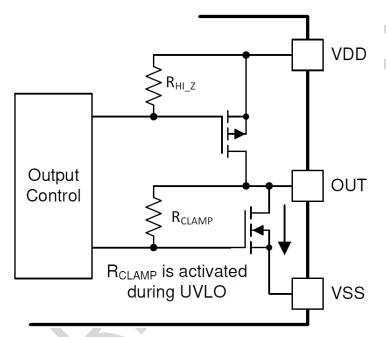

The CMT8602X has an internal under voltage lock out (UVLO) protection feature on each supply voltage between the VDD and VSS pins for both outputs. When the VDD bias voltage is lower than  $V_{VDD_ON}$  at device start-up or lower than  $V_{VDD_OFF}$  after start-up, the VDD UVLO feature holds the channel output low, regardless of the status of the input pins.

When the output stages of the driver are in an unbiased or UVLO condition, the driver outputs are held low by an active clamp circuit that limits the voltage rise on the driver outputs (illustrated in the figure below). In this condition, the upper PMOS is resistively held off by  $R_{Hi-Z}$  while the lower NMOS gate is tied to the driver output through  $R_{CLAMP}$ . In this configuration, the output is effectively clamped to the threshold voltage of the lower NMOS device, typically around 1.75 V, regardless of whether bias power is available.

Figure 4-2. Simplified Representation of Active PullDown Feature

The VDD UVLO protection has a hysteresis feature ( $V_{VDD_HYS}$ ). This hysteresis prevents chatter when there is ground noise from the power supply. This also allows the device to accept small drops in bias voltage, which commonly occurs when the device starts switching and operating current consumption increases suddenly.

The inputs of the CMT8602X also have internal under voltage lock out (UVLO) protection feature. The inputs cannot affect the outputs unless the supply voltage VCCI exceeds  $V_{VCCI_ON}$  on start-up. The outputs are held low and cannot respond to inputs when the supply voltage VCCI drops below  $V_{VCCI_OFF}$  after start-up. Like the UVLO for VDD, there is hysteresis ( $V_{VCCI_HYS}$ ) to ensure stable operation.

|                                                        | INF | PUTS | OUTPUTS |      |  |

|--------------------------------------------------------|-----|------|---------|------|--|

| CONDITION                                              | INA | INB  | OUTA    | OUTB |  |

| VCCI-GND < V <sub>VCCI_ON</sub> during device start up | Н   | L    | L       | L    |  |

| VCCI-GND < $V_{VCCI_{ON}}$ during device start up      | L   | Н    | L       | L    |  |

| VCCI-GND < V <sub>VCCI_ON</sub> during device start up | Н   | Н    | L       | L    |  |

| VCCI-GND < V <sub>VCCI_ON</sub> during device start up | L   | L    | L       | L    |  |

| VCCI-GND < V <sub>VCCI_OFF</sub> after device start up | Н   | L    | L       | L    |  |

| VCCI-GND < V <sub>VCCI_OFF</sub> after device start up | L   | Н    | L       | L    |  |

#### Table 4-1. VCCI UVLO Feature Logic

| VCCI-GND < V <sub>VCCI_OFF</sub> after device start up | Н | Н | L | L |

|--------------------------------------------------------|---|---|---|---|

| VCCI-GND < V <sub>VCCI_OFF</sub> after device start up | L | L | L | L |

#### Table 4-2.VDD UVLO Feature Logic

| CONDITION                                            | INP | UTS | OUTPUTS |      |  |

|------------------------------------------------------|-----|-----|---------|------|--|

|                                                      | INA | INB | OUTA    | OUTB |  |

| VDD-VSS < $V_{VDD_ON}$ during device start up        | Н   | L   | L       | L    |  |

| VDD-VSS < $V_{VDD_ON}$ during device start up        | L   | Н   | L       | L    |  |

| VDD-VSS < V <sub>VDD_ON</sub> during device start up | Н   | Н   | L       | L    |  |

| VDD-VSS < V <sub>VDD_ON</sub> during device start up | L   | L   | L       | L    |  |

| VDD-VSS < $V_{VDD_ONF}$ after device start up        | Н   | L   | L       | L    |  |

| $VDD-VSS < V_{VDD_ONF}$ after device start up        | L   | Н   | L       | L    |  |

| VDD-VSS < $V_{VDD_ONF}$ after device start up        | Н   | Н   | L       | L    |  |

| VDD-VSS < $V_{VDD_ONF}$ after device start up        | L   | L   | L       | L    |  |

#### 4.3.2 Input and Output Logic Table

Assume VCCI, VDDA, VDDB are powered up. The following table shows the operation with INA, INB and DIS and the corresponding output state.

| INP       | UTS       |     | OUT  | PUTS | NOTE                                                                                     |

|-----------|-----------|-----|------|------|------------------------------------------------------------------------------------------|

| INA       | INB       | DIS | OUTA | OUTB | ΝΟΤΕ                                                                                     |

| L         | L         | L   | L    | L    |                                                                                          |

| L         | Н         | L   | L    | н    | If the dead time function is used, output transitions occur after the dead time expires. |

| Н         | L         | L   | Н    | L    |                                                                                          |

| Н         | Н         | L   | L    | L    | DT is programmed with R <sub>DT</sub> .                                                  |

| Н         | Н         | L   | Н    | н    | DT pin pulled high to $V_{CCL}$                                                          |

| Left Open | Left Open | L   | L    | L    |                                                                                          |

| х         | х         | н   | L    | Ľ    |                                                                                          |

| Notes:    |           |     |      |      |                                                                                          |

#### Table 4-3. INPUT/OUTPUT Logic Table <sup>[1][2]</sup>

[1]. "X" means L, H or left open.

[2]. For improved noise immunity, recommend connecting INA, INB, and DIS to GND, and DT to VCCI, when these pins are not used.

### 4.3.3 Input Stage

The input pins (INA, INB, and DIS) of the CMT8602X is based on a TTL and CMOS compatible input- threshold logic that is totally isolated from the VDD supply voltage of the output channels. The input pins are easy to drive with logic-level control signals (such as those from 3.3-V microcontrollers), since the CMT8602X has a typical high threshold ( $V_{INAH}$ ) of 1.8 V and a typical low threshold of 1 V, which vary little with temperature. A wide hysteresis ( $V_{INA_{-}HYS}$ ) of 0.8 V makes for good noise immunity and stable operation. If any of the inputs are ever left open, internal pull-down resistors force the pin low. These resistors are typically 200 k $\Omega$ . HOPE recommends grounding any unused inputs.

The amplitude of any signal applied to the inputs should not exceed the voltage at the  $V_{CCI}$  pin. The CMT8602X cannot be driven from an analog controller with an output voltage greater than the  $V_{CCI}$  voltage.

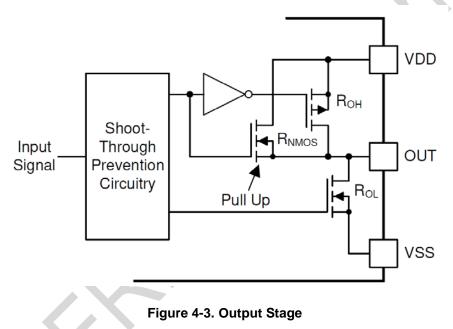

### 4.3.4 Output Stage

The CMT8602X output stage features a pull-up structure which delivers the highest peak-source current when it is most needed during the Miller plateau region of the power-switch turn on transition (when the power switch drain or collector voltage experiences  $d_V/d_t$ ). The output stage pull-up structure features a P-channel MOSFET and an additional pull-up N-channel MOSFET in parallel. The function of the N-channel MOSFET is to provide a boost in the peak-sourcing current, enabling fast turn on. This is accomplished by briefly turning on the N-channel MOSFET during a narrow instant when the output is changing states from low to high.

The  $R_{OH}$  parameter is a DC measurement and it is representative of the on-resistance of the P-channel device only. This is because the pull-up N-channel device is held in the off state in DC condition and is turned on only for a brief instant when the output is changing states from low to high. Therefore, the effective resistance of the CMT8602X pull-up stage during this brief turn-on phase is much lower than what is represented by the R<sub>OH</sub> parameter.

The pull-down structure of the CMT8602X is composed of an N-channel MOSFET. The  $R_{OL}$  parameter, which is also a DC measurement, is representative of the impedance of the pull-down state in the device. The output voltage swings between VDD and VSS for rail-to-rail operation.

### 4.4 Device Functional Modes

#### 4.4.1 Disable Pin

Setting the DISABLE pin high shuts down both outputs simultaneously. Grounding (or left open) the DISABLE pin allows the device to operate normally. The DISABLE response time is in the range of 40 ns and quite responsive, which is as fast as propagation delay. The DISABLE pin is only functional (and necessary) when VCCI stays above the UVLO threshold. It is recommended to tie this pin to ground if the DISABLE pin is not used to achieve better noise immunity, and it is recommended to bypass using a  $\approx$ 1nF low ESR/ESL capacitor close to DIS pin when connecting DIS pin to a micro controller with distance.

#### 4.4.2 Programmable Dead Time (DT) Pin

The CMT8602X allows the user to adjust dead time (DT) in the following ways:

#### 4.4.2.1 Connecting a Programming Resistor between DT and GND Pins

One can program  $t_{DT}$  by placing a resistor,  $R_{DT}$ , between the DT pin and GND. The appropriate  $R_{DT}$  value can be determined from foemula (1), where  $R_{DT}$  is in  $k\Omega$  and  $t_{DT}$  is in ns

#### $t_{\text{DT}} \approx 10 * R_{\text{DT}} \quad (1)$

The steady state voltage at DT pin is around 0.8 V, and the DT pin current will be less than 10uA when  $R_{DT}$ =100k $\Omega$ . When using  $R_{DT}$ > 5k $\Omega$ , it is recommended to parallel a ceramic capacitor, 2.2nF or above, close to the chip with  $R_{DT}$  to achieve better noise immunity and better dead time matching between two channels. It is not recommended to leave the DT pin floating.

An input signal's falling edge activates the programmed dead time for the other signal. The output signals' dead time is always set to the longer of either the driver's programmed dead time or the input signal's own dead time. If both inputs are high simultaneously, both outputs will immediately be set low. This feature is used to prevent shoot-through, and it doesn't affect the programmed dead time setting for normal operation. Various driver dead time logic operating conditions are illustrated and explained in the following figure:

#### Figure 4-4. Input and Output Logic Relationship with Input Signals

**Condition A:** INB goes low, INA goes high. INB sets OUTB low immediately and assigns the programmed dead time to OUTA. OUTA is allowed to go high after the programmed dead time.

**Condition B:** INB goes high, INA goes low. Now INA sets OUTA low immediately and assigns the programmed dead time to OUTB. OUTB is allowed to go high after the programmed dead time.

**Condition C:** INB goes low, INA is still low. INB sets OUTB low immediately and assigns the programmed dead time for OUTA. In this case, the input signal dead time is longer than the programmed dead time. When INA goes high after the duration of the input signal dead time, it immediately sets OUTA high.

**Condition D:** INA goes low, INB is still low. INA sets OUTA low immediately and assigns the programmed dead time to OUTB. In this case, the input signal dead time is longer than the programmed dead time. When INB goes high after the duration of the input signal dead time, it immediately sets OUTB high.

**Condition E:** INA goes high, while INB and OUTB are still high. To avoid overshoot, OUTB is immediately pulled low. After some time OUTB goes low and assigns the programmed dead time to OUTA. OUTB is already low. After the programmed dead time, OUTA is allowed to go high.

**Condition F:** INB goes high, while INA and OUTA are still high. To avoid overshoot, OUTA is immediately pulled low. After some time OUTA goes low and assigns the programmed dead time to OUTB. OUTA is already low. After the programmed dead time, OUTB is allowed to go high.

# **5** Application and Implementation

### 5.1 Application Information

The CMT8602X effectively combines both isolation and buffer-drive functions. The flexible, universal capability of the CMT8602X (with up to 5.5-V VCCI and 30-V VDDA/VDDB) allows the device to be used as a low-side, high-side, high-side/low-side or halfbridge driver for MOSFETs, IGBTs or GaN transistor. With integrated components, advanced protection features (UVLO, dead time, and disable) and optimized switching performance, the CMT8602X enables designers to build smaller, more robust designs for enterprise, telecom, automotive, and industrial applications with a faster time to market.

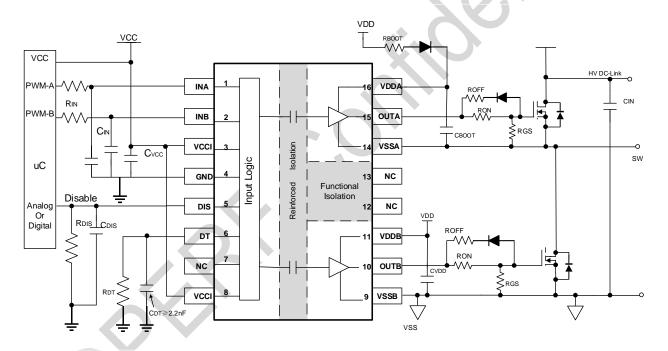

### 5.2 Typical Application

The circuit in the figure below shows a reference design with the CMT8602X driving a typical half-bridge configuration which could be used in several popular power converter topologies such as synchronous buck, synchronous boost, half-bridge/full bridge isolated topologies, and 3-phase motor drive applications.

# 6 Power Supply Recommendations

The recommended input supply voltage (V<sub>CCI</sub>) for the CMT8602X is between 3 V and 5.5 V. The output bias supply voltage (V<sub>DDA</sub>/V<sub>DDB</sub>) ranges from 9 V to 30 V. The lower end of this bias supply range is governed by the internal under voltage lockout (UVLO) protection feature of the device. V<sub>DD</sub> and V<sub>CCI</sub> must not fall below their respective UVLO thresholds during normal operation. The upper end of the V<sub>DDA</sub>/V<sub>DDB</sub> range depends on the maximum gate voltage of the power device being driven by the CMT8602X. The recommended maximum V<sub>DDA</sub>/V<sub>DDB</sub> is 30 V.

A local bypass capacitor should be placed between the  $V_{DD}$  and  $V_{SS}$  pins. This capacitor should be positioned as close to the device as possible. A low ESR, ceramic surface mount capacitor is recommended. It is further suggested that one place two such capacitors: one with a value of  $\approx 10 \,\mu$  F for device biasing, and an additional  $\leq 100$  nF capacitor in parallel for high frequency filtering.

Similarly, a bypass capacitor should also be placed between the  $V_{CCI}$  and GND pins. Given the small amount of current drawn by the logic circuitry within the input side of the CMT8602X, this bypass capacitor has a minimum recommended value of 100 nF.

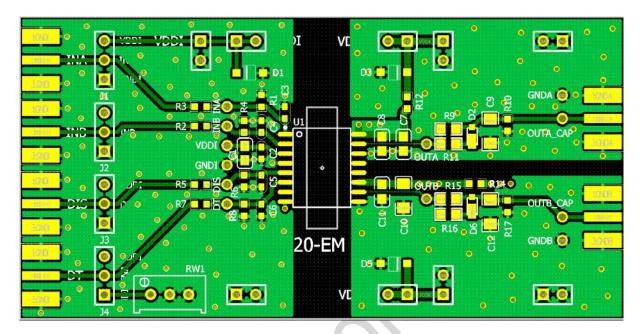

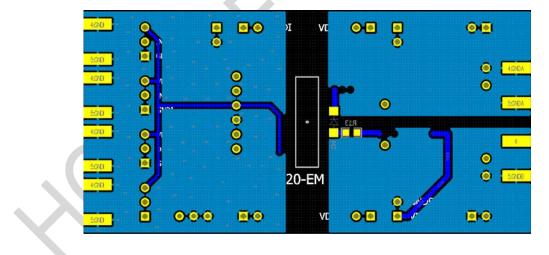

# 7 PCB Layout